HDI PCB阶数终极指南:从单层到八层板选型策略与成本优化

发布时间:2025/7/15 14:34:06

为什么HDI阶数决定PCB成败?

在智能手机等高端设备中,其PCB电路板的HDI阶数每提升一级,布线密度则可增加60%-70%(IPC-2226标准数据)。但阶数选择错误可能导致:

· 成本超支40%以上(二阶 vs 三阶HDI对比)

· 信号损耗增加 >3dB @10GHz

· 良率下降15%-30%

阶数定义与核心参数公式

激光微孔技术的关键指标

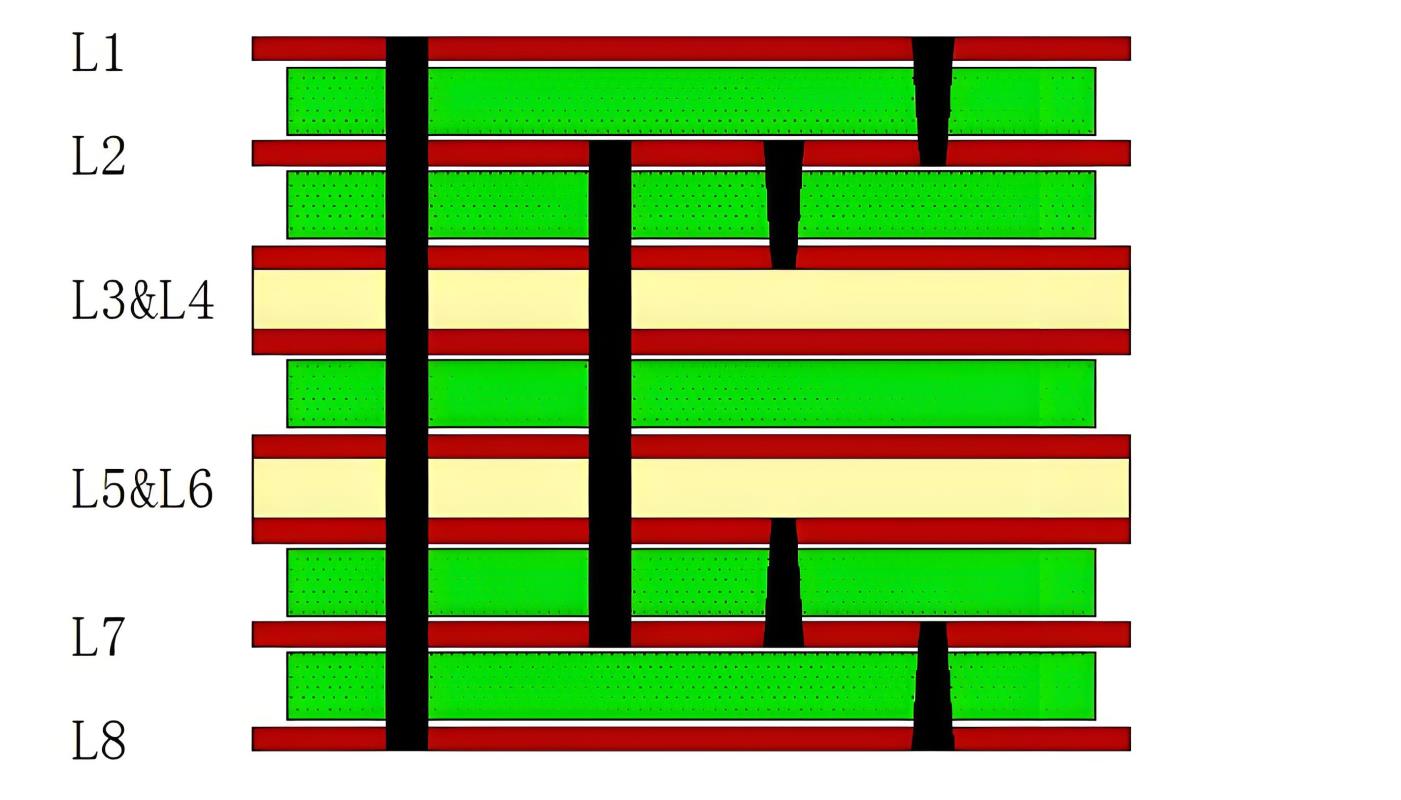

HDI阶数由 N = (Lv - 1) + ΣMi 定义(Lv为层数,Mi为微孔层数)。例如:

· 一阶HDI:仅L1-L2含激光孔

· 二阶叠孔:L1-L2 & L2-L3双激光孔堆叠

· 二阶错孔:L1-L2 & L1-L3错位微孔

按层数详解HDI选型策略

双面板(2层)消费电子设计

· 推荐阶数:一阶HDI (成本降低25% vs二阶)

· 典型应用:智能电视控制板、蓝牙耳机PCBA

· 布线密度:≥8线/mm

· 供应商建议:选择像深圳联益这样的具备 ≤100μm微孔能力的PCBA厂商

四层板高速信号处理方案

· 黄金配置:一阶HDI (覆盖90% LVDS/PCIe场景)

· 成本警报:二阶HDI导致成本激增30%(板材+钻孔工艺)

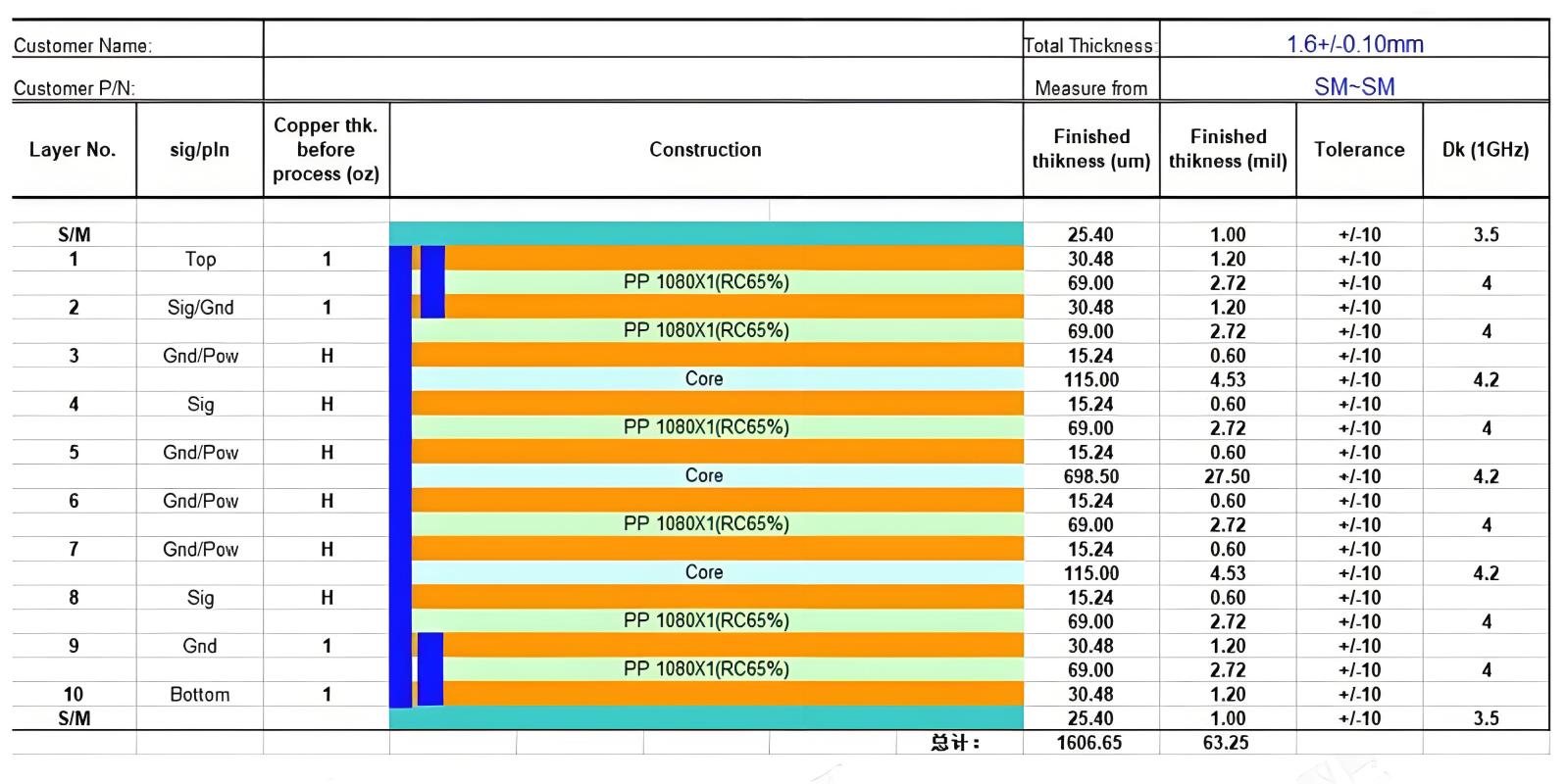

· 阻抗控制公式:

![]()

(H:介质厚度, W:线宽, T:铜厚, ε_r:介电常数)

六层板工业级可靠性设计

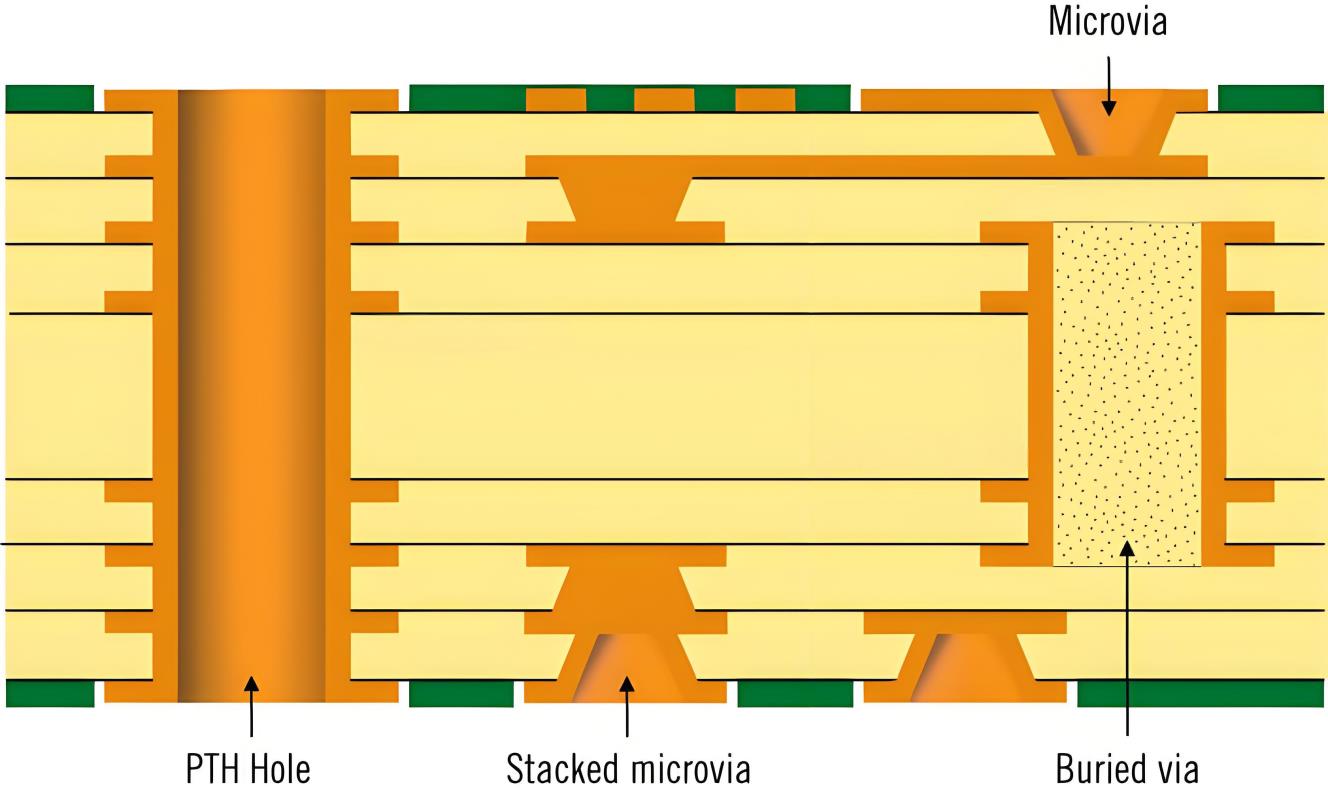

· 最优解:二阶HDI(盲埋孔组合)

· 密度提升:比一阶增加50%布线空间

· 成本对比表:

|

阶数 |

单价增幅 |

良率 |

适用场景 |

|

一阶 |

基准 |

98% |

普通工控设备 |

|

二阶 |

+45% |

95% |

通信基站PCBA |

|

三阶 |

+110% |

88% |

航天军用电子 |

八层板超高端设备必备方案

· 强制配置:三阶HDI(支持0.4mm BGA间距)

· 元件密度:≥1200 pins/cm²(智能手机PCB标准)

· 信号损耗测试数据:

阶数 | 插入损耗@10GHz | 回波损耗

-------|----------------|----------

二阶 | -2.1dB/cm | -18dB

三阶 | -1.3dB/cm | -26dB

三大选型法则与供应商合作策略

成本优先原则(六层以下板)

· 一阶HDI满足:USB3.0/DDR3以下速率的信号完整性

· 避免过度设计:每增加一阶,工程费增加$200-$500

密度驱动设计(八层板以上)

· 三阶HDI实现:0.1mm/0.1mm线宽线距

· 微孔尺寸:≤75μm(标准FR4加工极限)

高速信号保真技术

· 延时匹配公式:

![]()

· 差分对长度公差:≤5mil

H2:立即下单定制化您的HDI解决方案

行动号召:

如您有HDI板的生产需求,请转至UG商城PCB在线下单页面,提交您PCB Gerber设计文件,24小时内获取有竞争力的PCBA报价。