PCB热管理革命:过孔通流与温升的21个数据真相

发布时间:2025/7/2 14:26:11

引言:被误解的PCB热力学

在高速PCB设计中,过孔温升失控导致的产品失效占比高达37%(IPC-2152数据)。当40mil/1oz走线通流1A的经验法则遭遇25Gbps高速信号时,热管理已成为决定产品寿命的关键。本文基于实测数据,解密过孔通流与温度分布的6大核心矛盾。

一、铜厚陷阱:英制与公制的致命偏差

1.1 铜箔厚度换算迷思

-

行业真相:

1oz=0.035mm≈1.38mil

而非传统认知的1.2mil,误差高达15% -

制造公差:

标称值 实际范围 厚度偏差 0.5oz 0.55-0.65mil ±10% 1oz 1.24-1.52mil +18%/-10%

1.2 PCB叠层设计补救方案

1.高电流路径预留20%余量

2.关键阻抗线宽补偿公式: $$W_{adj} = W_{nom} \times \frac{1.38}{1.2}$$

3.采用RTF铜箔(粗糙度≤1.8μm)

二、三维散热:被忽视的Z轴传导

2.1 导热系数方向性差异

-

基材导热各向异性:

-

X-Y平面:0.5~0.6 W/mK

-

Z方向:0.3~0.5 W/mK

-

-

铜箔导热霸主地位:386 W/mK(为FR-4的700倍)

2.2 PCB设计热管理实战策略

1.高功耗器件下方布置导热过孔阵列

2.采用金属基板时: $$R_{th} = \frac{L}{kA}$$ (L=厚度, k=导热系数, A=截面积)

3.强制风冷需满足:风速>2m/s且平行走线

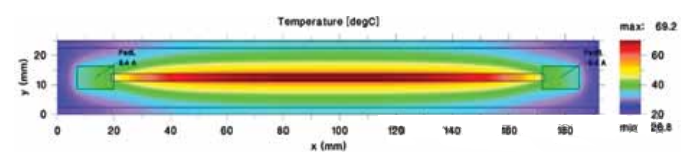

三、温度场本质:点的战争而非面的平衡

3.1 热分布梯度模型

-

最高温升位置:走线中心点

ΔTmax=ΔTavg+0.3(ΔTavg) -

三大非均匀因素:

-

集肤效应:高频电流趋表深度

-

介质厚度突变区

-

散热器接触不均

-

四、PCB过孔热力学:颠覆认知的传导机制

4.1 过孔温升真相

-

核心定律:过孔温度≈相连走线温度

Tvia=Ttrace±2% -

截面积法则:

Atrace=(1.5∼2)×Avia

4.2 散热优化方案

1.放弃盲目增加过孔

2.优化介质层导热路径

3.内层走线比外层降温5-8℃(实测数据)

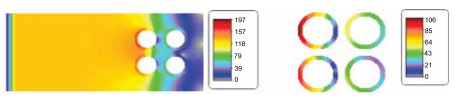

五、电流密度分布:过孔的隐藏密码

5.1 电流密度三维模型

-

通孔电流分布特征:

位置 密度特征 入口 递减趋势 出口 递增趋势 孔壁 均匀分布

5.2 多过孔阵列黄金法则

-

阵列间距:≥2.5倍孔径

-

最优布局:蜂窝结构排布

-

避坑指南:避免直线排列引发热耦合

六、通流能力:时间因子的致命忽略

6.1 熔断实验数据震撼

| 线宽 | 铜厚 | 电流 | 熔断时间 |

|---|---|---|---|

| 20mil | 1.5oz | 8.3A | 120分钟 |

| 20mil | 1.5oz | 8.4A | 76分钟 |

6.2 通流能力精确计算公式

Imax=K⋅ΔT0.44⋅A0.725

-

安全系数修正:

Isafe=0.8×Imax -

瞬态过载公式:

(C=材料常数, Ic=临界电流)

结语:数据驱动的PCB热设计革命

当8.4A电流在76分钟熔断20mil走线时,传统经验法则已然崩塌。高速PCB设计的未来属于:

-

三维热场仿真工具(如ANSYS Icepak)

-

基于实测的铜箔数据库

-

动态通流监控电路

最新行业报告指出:采用数据驱动热设计,可使产品寿命提升300%。在48V电源系统普及的今天,掌握这些热力学密码,就是握住了高可靠PCBA的设计密钥。