🔍 深入亚微米战场:PCB信号完整性的电路、布线、仿真决胜指南

发布时间:2025/6/25 14:31:55

在深亚微米工艺主导的电子时代,信号完整性(Signal Integrity, SI) 已从设计挑战升级为决定系统成败的核心要素。当晶体管开关速度进入皮秒级,接地反弹(Ground Bounce)、串扰(Crosstalk)、时序紊乱(Timing Violation) 等问题如同潜伏的杀手,随时可能让高性能芯片和高速PCB功亏一篑。传统的经验法则和试错方法在GHz级信号面前已然失效。本文将深入剖析电路设计、PCB布线、建模仿真三大关键战场,提供一套系统化、可落地的PCB信号完整性解决方案,助您在高速数字设计的复杂迷局中精准制胜!

🛠️ 一、PCB电路设计:从源头扼杀SI风险

高速系统的信号完整性之战,始于芯片和电路设计阶段。源头管控是最高效的策略。

⚡ 1.1 边沿速率(Slew Rate)的精准管控

信号的上升/下降时间(Tr/Tf)是SI问题的核心引爆点。过快的边沿速率(Slew Rate = dV/dt ≈ 0.8 / Tr (for 20%-80%))会急剧放大反射、串扰和电源噪声。策略:

-

设定阈值:根据传输线阻抗(Z0)和负载特性,为关键信号(如时钟、高速数据总线)设定最大允许的dV/dt或dI/dt值。例如,在50Ω系统中,将时钟信号的Tr控制在信号周期(T)的7%-10%通常是安全起点(Tr ≥ 0.07T)。

-

强制差分:对时钟、高速串行链路(如PCIe, USB, SATA)等关键信号,必须采用差分信号传输技术(ECL, LVDS, CML)。差分对的抗共模噪声能力是单端信号的指数级提升,实测表明,在相同环境下,LVDS差分对的共模抑制比(CMRR)可达60dB以上,远超单端信号。

🎯 1.2 端接策略的精准打击

阻抗失配引发的反射是信号畸变的元凶。正确的端接是消除反射的“外科手术刀”。

-

串联电阻端接(Source Series Termination):在驱动器输出端串联电阻(Rs ≈ Z0 - Rout,通常10Ω~33Ω),使源端阻抗与传输线阻抗匹配。关键:电阻必须紧贴驱动芯片引脚放置,任何额外电感都会严重降低效果。

-

并联端接(Parallel Termination):在接收端并联电阻(Rt = Z0)到地或电源(需考虑直流功耗)。对于阻尼振铃(Ringing),可在Rt上并联小电容(Ct < 50pF) 构成RC端接,但需警惕电容和引脚本身的寄生电感(L_pkg)形成谐振,其谐振频率 f_res ≈ 1/(2π√(L_pkg*Ct)) 可能落入信号带宽内造成恶化。

🔋 1.3 电源完整性(PI)的协同设计

SI与PI是硬币的两面。电源噪声(ΔI噪声、地弹)会直接耦合到信号网络。

-

封装级去耦:在芯片封装基板或邻近PCB层上,为每个电源/地引脚对配置去耦电容阵列。经典的组合是0.1μF (100nF) + 1μF (或10μF)。0.1μF针对高频噪声(MHz-GHz),1/10μF针对中低频噪声(KHz-MHz)。电容的等效串联电感(ESL) 是关键参数,优选超低ESL(<0.5nH)的陶瓷电容(如X7R, X5R)。

-

芯片级储能:在芯片内部的电源分布网络(PDN)中,利用相邻金属层(如Mx和Mx+1)的重叠区域形成片上金属-绝缘层-金属(MIM)电容或深槽电容(Deep Trench Cap),为高速逻辑门瞬间切换提供最近的、超低阻抗(Z_local = √(L_pkg / C_onchip))的电流通路,有效抑制局部电压塌陷(IR Drop)和地弹噪声。

🧩 二、合理布线:PCB层面的空间战争

PCB布线是将电路设计意图转化为物理现实的关键战场,是信号完整性的“第二道防线”。

📶 2.1 拓扑约束优先法则

信号在网络中的“行走路径”至关重要。

-

高速信号(>1Gbps)强制拓扑:必须采用点对点(Point-to-Point) 或 菊花链(Daisy Chain) 结构。严格避免T型分支(T-branch),因其会引入严重的阻抗不连续和分支线反射。对于多点负载(如DDR内存),远端簇(Fly-by)拓扑已成为业界标准,能显著改善信号质量。

-

布线几何规范:严禁直角走线!直角拐角会增大走线有效宽度,导致局部电容增大,阻抗降低(可达ΔZ ≈ -20%),形成反射源。必须使用45°斜角或更优的圆弧倒角(Curved Bend)。研究表明,圆弧倒角可将阻抗不连续性降至最低。

⚖️ 2.2 间距与层叠策略

控制串扰和提供稳定回流路径是核心目标。

-

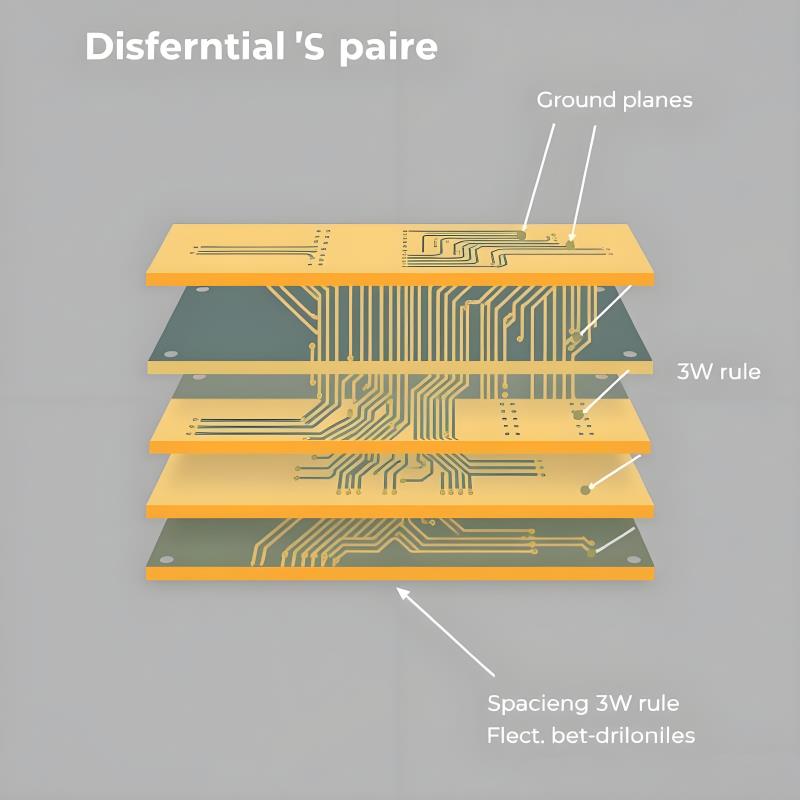

差分对控制:差分对内间距(S)通常为S ≤ 2W(W为线宽),以保持紧密耦合。差分对间间距(D)应满足D ≥ 3W(最好≥ 5W),并确保参考平面完整。遵循3W规则可有效抑制近端串扰(NEXT)达 >6dB。关键高速差分对(如25G+ SerDes)可能需要4W甚至更大间距。

-

层叠设计与电源完整性:核心原则:为每个高速信号层提供相邻的完整参考平面(电源或地)。推荐采用对称叠层结构以减小板弯翘曲。电源层与地层应紧密耦合(如使用2-4mil薄介质),形成高效平板电容,显著降低高频电源阻抗。对于大电流路径,使用1oz(35μm)或更厚的铜箔能有效降低直流压降(V_drop = I * R_trace)。

🕳️ 2.3 过孔残桩(Stub)的致命陷阱与处理

过孔是高速PCB的“必要之恶”,其产生的残桩Stub是高频信号(>5GHz)的隐形杀手。Stub相当于一段终端开路的传输线,在特定频率(f_res ≈ c / (4 * Length_stub * √εr),c为光速,εr为介质常数)会产生谐振,导致信号在该频点附近产生巨大插入损耗(陷波)。

-

背钻(Back Drilling):首选解决方案。使用特殊钻头从PCB背面将过孔中未使用的导电柱(即Stub)钻掉。要求残桩长度控制 <10mil(0.25mm) 以内。这对于10Gbps+信号至关重要。

-

禁用测试点过孔:在最终版本的高速信号线上,绝对禁止为了测试方便而添加的未连接测试点过孔。它们会引入显著的Stub效应。测试点应通过短分支线引出(并做端接),或使用专用无源探头点。

🧪 三、建模仿真:设计阶段的数字孪生

在物理PCB制造之前,利用精确的模型和强大的仿真工具构建“数字孪生体”,是预见和解决SI/PI问题的最高效、最经济手段。

🔬 3.1 模型精度分级:仿真的基石

垃圾输入,垃圾输出(GIGO)。模型精度决定仿真可信度。

-

IBIS-AMI模型(Algorithmic Model Interface):行业标准,用于高速串行链路(SerDes)的发送器(Tx)和接收器(Rx)行为级建模。包含I/V、V/t曲线以及均衡(CTLE, DFE, FFE)等算法的可执行模块。优势:保密芯片晶体管级细节,仿真速度快。

-

SPICE模型:基于晶体管级网表的精确电路模型。适用于关键IP核(如PLL, 高速IO Buffer)、无源元件(R, L, C) 及板级互连简化模型的详细时域分析。精度高,但仿真速度慢,复杂度高。

-

S参数模型(Scattering Parameters):表征线性无源互连结构(传输线、过孔、连接器)频响特性的黄金标准。通过矢量网络分析仪(VNA)测量或电磁场(EM)仿真提取。包含幅值和相位信息(S11, S21, S12, S22...),直接反映插入损耗(IL = -20log10|S21| dB)、回波损耗(RL = -20log10|S11| dB)等关键指标。S参数模型是进行通道分析的基础。

🧪 3.2 仿真场景全覆盖:挑战设计极限

单一场景仿真不足以暴露所有风险。

-

静态分析:

-

设计规则检查(DRC):自动检查布线是否违反间距、线宽、长度匹配(如DDR DQS-DQ skew < 25ps)等约束。

-

拓扑与阻抗验证:提取网络拓扑,计算走线特征阻抗(Z0 ≈ (87/√(εr+1.41)) * ln(5.98H/(0.8W+T)) Ω,H为到参考平面高度,W线宽,T铜厚),检查是否达标(如50Ω±10%)。

-

-

动态分析:

-

时域反射/传输(TDR/T):直观显示阻抗不连续点位置和程度(分辨率可达ps级)。

-

眼图分析(Eye Diagram):评估高速串行链路性能的核心手段。将大量比特位的信号叠加显示,形成“眼图”。通过测量眼高(Eye Height)、眼宽(Eye Width)、抖动(Jitter) 并对比眼图模板(Eye Mask) 判断是否合格。要求模板余量(Mask Margin)>20% 以保证足够系统裕量。

-

-

极端场景压力测试:

-

电源波动(±5%甚至±10%):模拟电源电压最坏情况,检查时序、噪声容限。

-

温度循环(-40℃ ~ 125℃):考虑材料参数(Dk, Df)、导体电阻随温度变化的影响。

-

工艺角(Process Corner):考虑器件和互连制造公差带来的性能偏差。

-

🔄 3.3 迭代优化闭环:仿真驱动设计(SDD)

仿真的终极价值在于指导并优化设计。

-

约束驱动布线(Constraint-Driven Routing):将仿真结果(如最大允许长度、匹配长度范围、间距要求、层分配)转化为具体的布线约束规则(Constraints),导入PCB设计工具(如Cadence Allegro, Mentor Xpedition)。设计师在布线过程中实时受到这些规则约束和指导,确保物理实现满足电气性能要求。

-

自动重布线引擎:对于仿真(如时序、串扰)失败的特定网络或区域,先进的EDA工具可基于设定的约束和优化目标,自动触发局部重布线或优化算法(如调整线长、线间距、换层、优化过孔位置),大幅提升设计效率。

💡 结语:征服信号完整性的系统工程

在深亚微米工艺和GHz级速度主宰的电子世界,信号完整性(SI)与电源完整性(PI) 的协同保障,已非锦上添花,而是关乎系统生死的核心技术。从芯片驱动设计(Slew Rate管控、差分传输、端接策略) 的源头把控,到PCB布局布线(拓扑约束、3W规则、层叠设计、背钻工艺) 的物理实现,再到建模仿真(IBIS-AMI/SPICE/S参数、眼图分析、约束驱动设计) 的前瞻验证,这是一场贯穿设计全流程、融合电路理论、电磁场分析与材料科学的系统工程。

唯有深刻理解高速信号在时域与频域的行为本质,精准运用本文所述的“电路、布线、仿真”三板斧,并持续关注先进封装(如2.5D/3D IC)、新材料(Low-Dk/Df, Ultra-Low Loss) 的发展,才能在日益严苛的高速PCB与PCBA设计中,确保信号的纯净、稳定与可靠,最终释放数字系统的巅峰性能。