PCB设计终极指南:掌握这7大EMI抑制技巧让电路板噪声直降40%

发布时间:2025/11/25 14:32:51

|在高速电路设计中,电磁干扰控制是决定产品成败的关键所在。

在当今高速电子设备中,电磁干扰(EMI)就像是一个隐形杀手,悄然威胁着产品的稳定性和可靠性。随着信号频率攀升至GHz级别,数字电路的上升时间已进入皮秒级,PCB设计中的电磁兼容问题变得愈发突出。

研究表明,不当的PCB布局和接地设计可使系统噪声电平增加20-40dB,而科学合理的防护措施则能显著降低这些干扰。本文将深入探讨PCB设计中的噪声产生机制,并提供一套实用有效的噪声抑制解决方案。

电磁干扰的物理溯源:认识看不见的敌人

在高速数字电路设计中,电源与地线系统产生的瞬态噪声是电磁干扰(EMI)的主要诱因。通过示波器可观测到电源线(Vcc)与地线(Vg)上的高频噪声电压,其本质源于逻辑器件状态切换时的瞬态电流突变。

1. 电源线噪声产生机制

以典型CMOS门电路为例:稳态阶段输出高/低电平时,上下MOS管交替导通,电源回路阻抗较高;而在瞬态切换时,Q3/Q4同时导通形成ns级低阻通路,产生30-100mA尖峰电流。

更关键的是电源线寄生电感(L≈5-20nH/cm)引发的感应电压,其大小可由公式 $V_{noise} = L \cdot \frac{di}{dt}$ 计算。例如,当di/dt达到100mA/ns时,仅1cm的电源走线就会产生0.5-2V的噪声电压,足以干扰低压数字电路的正常运行。

2. 地线噪声耦合路径

输出电平跳变时,地线电流$I_g$包含器件切换电流(主导低频分量)和寄生电容放电电流(主导高频分量)。地线电感产生的感应电压 $V_g$ 会反向耦合至信号回路,造成逻辑误触发。

实验数据显示,当信号频率超过10MHz时,地线阻抗主要来自感抗部分,而随着频率继续增加,地平面阻抗将成为制约系统性能的关键因素。

科学接地策略:构建安静的参考平面

混合接地系统的优化设计

在高速PCB设计中,接地方式的选择至关重要。根据电路特性选择合适的接地方式:

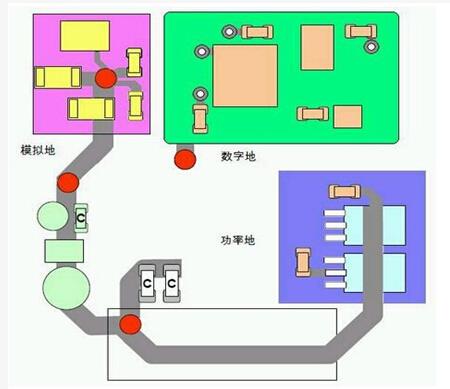

对于混合信号系统(同时包含模拟和数字电路),一个关键问题是:如何防止数字逻辑接地电流污染低电平模拟电路?传统方法采用分割地平面,但这会带来许多潜在问题,尤其是在大型复杂系统中。

更先进的方案是使用单个接地平面,将PCB分区为数字和模拟走线部分。模拟信号只能在电路板的模拟部分(任何层)上进行走线,而数字信号只能在电路板的数字部分(任何层)上进行走线。

这种方法的优势在于:数字接地返回电流需要直接返回信号走线下方——这是最低阻抗(最低电感)路径。数字地电流不会主动流向模拟地平面部分,因此只要布线规则得到严格遵守,数字噪声就不会干扰模拟信号。

多层PCB的接地平面技巧

对于高密度和高频率场合,多层PCB板是优选。根据经验法则,在高密度和高频率的场合通常使用四层电路板,就EMC而言比双面电路板好20DB以上。

在四层板设计中,其中一层应用作“全接地平面”,这不仅能降低接地阻抗,同时也能起到屏蔽作用。电源平面和接地平面应尽可能靠近相邻层放置,这样可以在整个板上产生大的PCB电容,为高频噪声提供低阻抗路径。

在接地过孔布置方面,关键信号线两侧应布置地孔,形成电磁屏蔽走廊。地过孔阵列密度应≥4个/cm²,这样能有效限制信号回流路径面积,减少辐射和耦合。

电源完整性设计:切断噪声传播途径

分层去耦电容策略

在高速PCB设计中,电源去耦电容远不止简单的滤波元件,它们实际上是维持电源完整性的第一道防线。去耦电容的作用类似于“迷你水库”,在芯片突然需要大电流时,能以极低的阻抗迅速释放储存的电荷。

实施分层去耦策略时应注意:

电源平面优化技术

电源平面的设计对控制EMI同样重要:

-

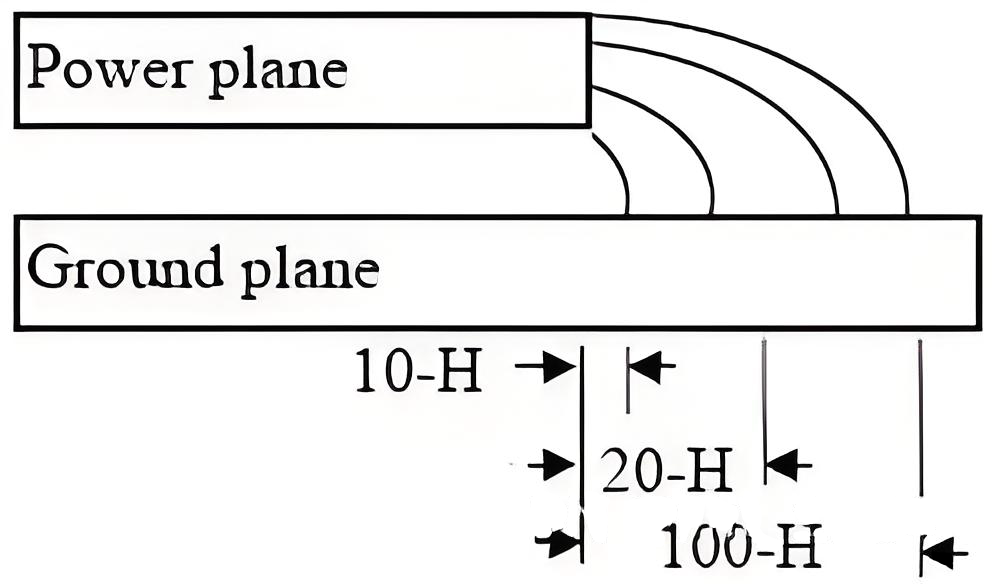

20H原则:电源层要相对地层内缩20H(H为两层间的间距),以减少边缘辐射效应。按照经验值,GND层相对板框内缩20mil(0.508mm),Power层相对板框内缩60mil(1.524mm),即电源相对地内缩40mil

阻抗连续性控制

随着数字电路速率及时钟频率的不断提高,在高速系统中,信号经过互连线时会产生延迟、反射、衰减、串扰、色散等信号完整性问题。对于传输速率达几百Mbps甚至数Gbps的高速数字信号,其有效频谱已扩展至微波甚至毫米波频段。

过孔是破坏阻抗连续性的主要因素之一。优化过孔设计包括:

差分信号布线原则

对于高速差分信号,应遵循特定设计原则:

信号回流控制

信号总是选择最低阻抗路径返回其源端,在高频情况下,这条路径是电感最低的路径——即紧邻信号线下方的参考平面。当信号切换参考平面时,会显著扩大回流路径面积,增加辐射。

为解决这个问题,可以在信号过孔附近添加接地过孔,或者在分割平面区域使用缝合电容(通常为10nF-100nF),为返回电流提供连续路径。

先进PCB布局技术:从经验到实践

3W/4W原则

为减少信号间的串扰,平行走线应遵循3W原则——即线与线之间保持3倍线宽的距离。如果要达到98%的电场不互相干扰,可使用10W规则。在设计中,如果因走线过密无法所有信号都满足3W,可优先对敏感信号(如时钟、复位信号)应用此规则。

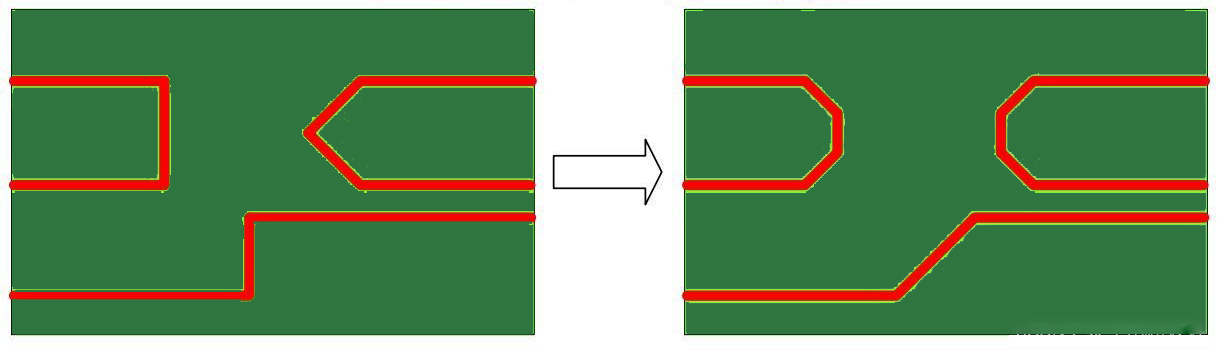

135度走线规则

在路由高速信号时,应尽量避免90度弯曲。在90度角,不能保证PCB蚀刻的精度,而且锋利边缘充当天线。建议使用135度走线弯曲,这样可以减少阻抗不连续性和外部辐射。

环路面积最小化

信号线与其回路构成的环面积应尽可能小,这也被称为环路最小规则。环面积越小,对外的辐射越少,接收外界的干扰也越小。在地平面分割和信号走线时,要考虑到地平面与重要信号走线的分布,防止由于地平面开槽等带来的问题。

案例研究:成功实施噪声抑制策略

某通信设备企业在设计一款支持5G信号的高速交换板时,初期原型在测试中出现了严重的电磁辐射问题,无法通过FCC认证。他们在接受了UG工程设计团队的综合噪声抑制策略后,成功将电路板噪声降低了40%。

采取的关键措施包括:

-

重新设计接地系统,采用单地平面结合分区布线策略,替代原分割地平面设计

-

优化去耦电容布局,确保每个电源引脚旁都有适当容值的小尺寸电容

-

为所有高速差分信号添加回流地过孔,减少阻抗不连续性

-

应用20H规则和3W原则,优化电源平面布局和信号间距

经过优化后,不仅EMI测试通过率大幅提升,信号完整性也有了明显改善,误码率降低了两个数量级。

结语

PCB电磁干扰控制是一项系统工程,需要从接地策略、电源设计、信号布线等多个维度综合考虑。科学的分区布局、恰当的接地方法、完善的去耦网络以及严格的阻抗控制,共同构成了高效EMI防护体系。

随着电子设备向更高速度、更高密度方向发展,EMC设计将面临更多挑战。掌握这些基础且有效的PCB噪声抑制技术,将使工程师在设计阶段就能预见并解决潜在的电磁兼容问题,缩短产品开发周期,提高产品可靠性。

本文内容由UG资深设计专家团队基于多年实战经验及实验数据整理。联系我们获取专业技术支持。