PCB可制造性设计(DFM)终极指南:从设计到量产一次成功

发布时间:2025/10/8 17:14:37

在电子产品日益精密化的今天,PCB可制造性设计(DFM)已成为连接设计与生产的核心桥梁。忽视DFM规则,不仅导致成本飙升,更可能使项目进度严重滞后。据统计,超过70%的PCB质量问题源于设计阶段的可制造性缺陷,而这些问题在生产过程中往往难以补救。

作为一名PCB设计师,掌握DFM原则意味着能够在图纸阶段预见并消除生产隐患,确保产品从设计到量产一次成功。

DFM为何成为PCB设计的必选项?

可制造性设计(Design for Manufacturability,简称DFM)是一套系统化的设计准则,旨在确保PCB设计符合生产厂商的工艺能力。它涵盖了从线宽线距、钻孔尺寸到层压结构和表面处理等各个方面。

当设计师忽视了制造商的能力极限,会发生什么?PCB生产商会发出DFM问题通知,整个项目陷入“设计-验证-修改”的死循环。这种重复工作不仅耗费时间和金钱,更可能导致市场机会的错失。实施DFM规则能最大限度地减少甚至完全避免板卡重做,排除布局更改、重新设计和重新验证板功能的必要性。

本质上,DFM分析是在PCB布局阶段就预先评估和最小化制造与组装过程中可能遇到的问题。在现代CAD工具中,通过输入制造约束条件,如最小线宽、最小间距等参数,设计规则检查(DRC)会自动标识出违规之处,使设计师能够在第一时间纠正错误。

PCB设计中的关键DFM检查点

钻孔设计:不可逆的工艺挑战

钻孔是PCB制造中最昂贵、最费力且不可逆的工序,发生在层压周期之后。钻孔DFM检查包括识别缺失孔、重复孔、残桩过孔和孔间距问题。

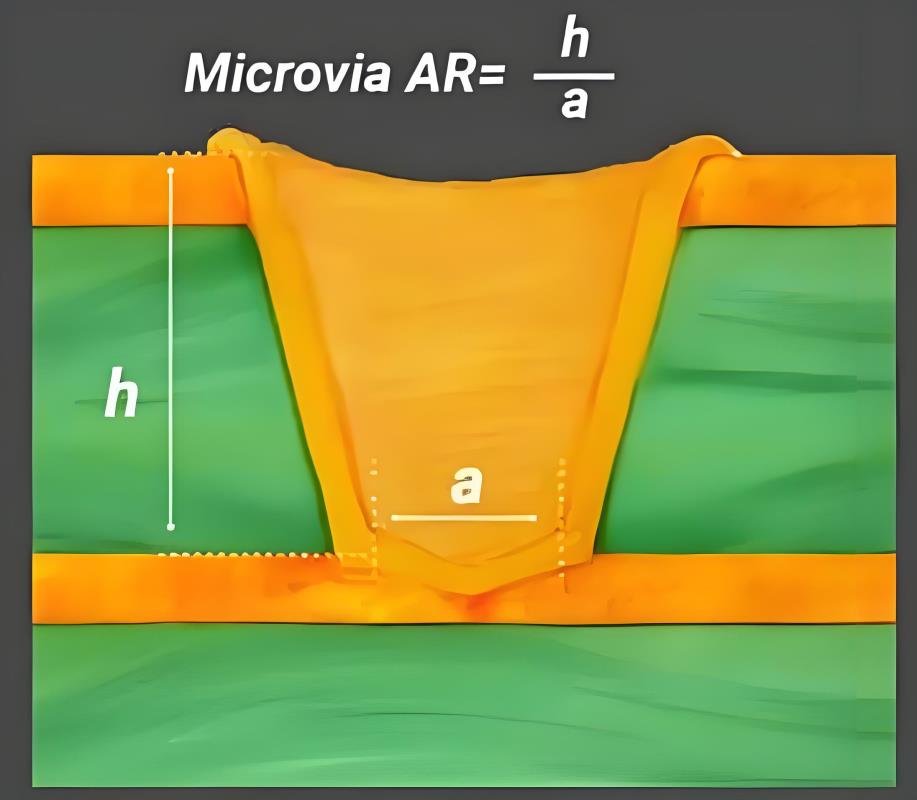

纵横比(AR)是钻孔深度与钻孔直径的比值,直接关系到电镀工艺的可行性。对于通孔,AR = PCB厚度/钻孔直径,典型值为1:10(适用于62mil厚度的板卡)。而对于微孔,AR = 钻孔深度(h)/ 钻孔直径(a),通常控制在0.75:1以内。

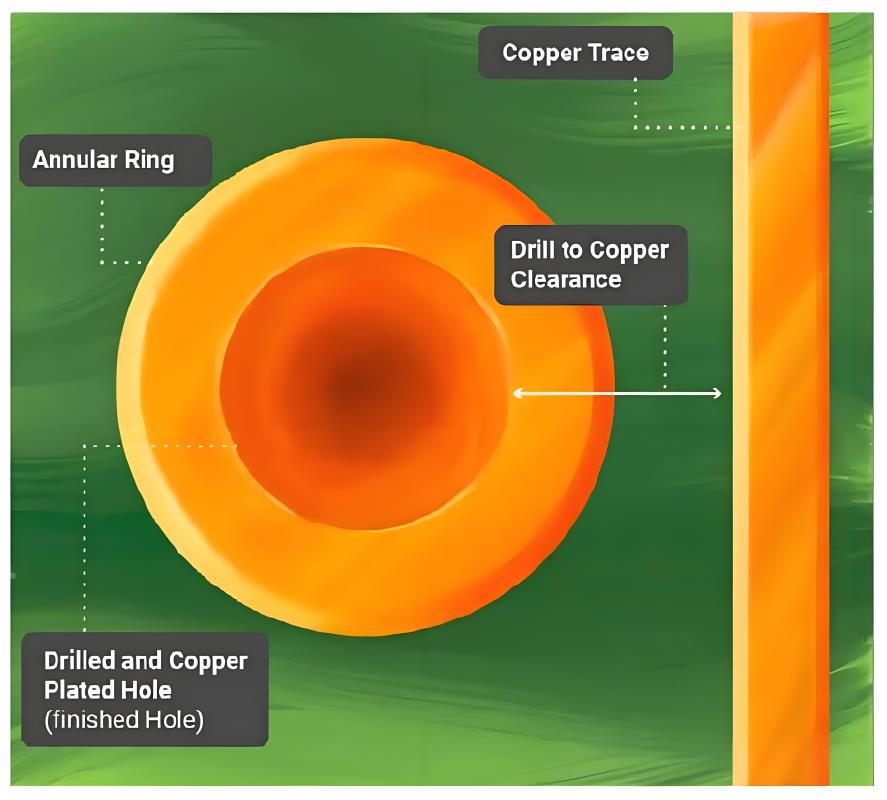

钻到铜的间距是另一个关键参数,它指的是钻孔边缘到最近铜特征(走线、铺铜等)的距离。计算公式为:成品孔到铜间隙 = 钻到铜间隙 + (电镀厚度 × 2)。举例来说,如果钻孔直径为6mil,电镀厚度为1mil,那么成品孔到铜间隙 = 6 + 1 × 2 = 8mil。

不足或不正确的环宽可能导致相切(环接触焊盘边缘)甚至 breakout(环超出焊盘)等致命缺陷。

PCB线路设计:平衡电气性能与制造能力

信号检查涵盖导体宽度、孔注册和间距要求等关键参数。根据IPC-2221C标准(2025年8月发布),内层允许电流的线宽计算公式使用k=0.024,而外层k=0.048。横截面积A = (电流I/(k×温升ΔT))¹/⁰·⁴⁴⁴,设计师可利用在线线宽与电流容量计算器简化此过程。

间距要求同样至关重要。合适的走线间隙能防止导体间闪络或击穿。例如,2oz铜厚的最小线间距应为8mils。此外,铜到板边间距(带电铜皮与PCB板边的距离)最好不小于0.3mm,如果是大面积铺铜,通常设为20mil的内缩距离。

阻焊设计:防止短路与氧化

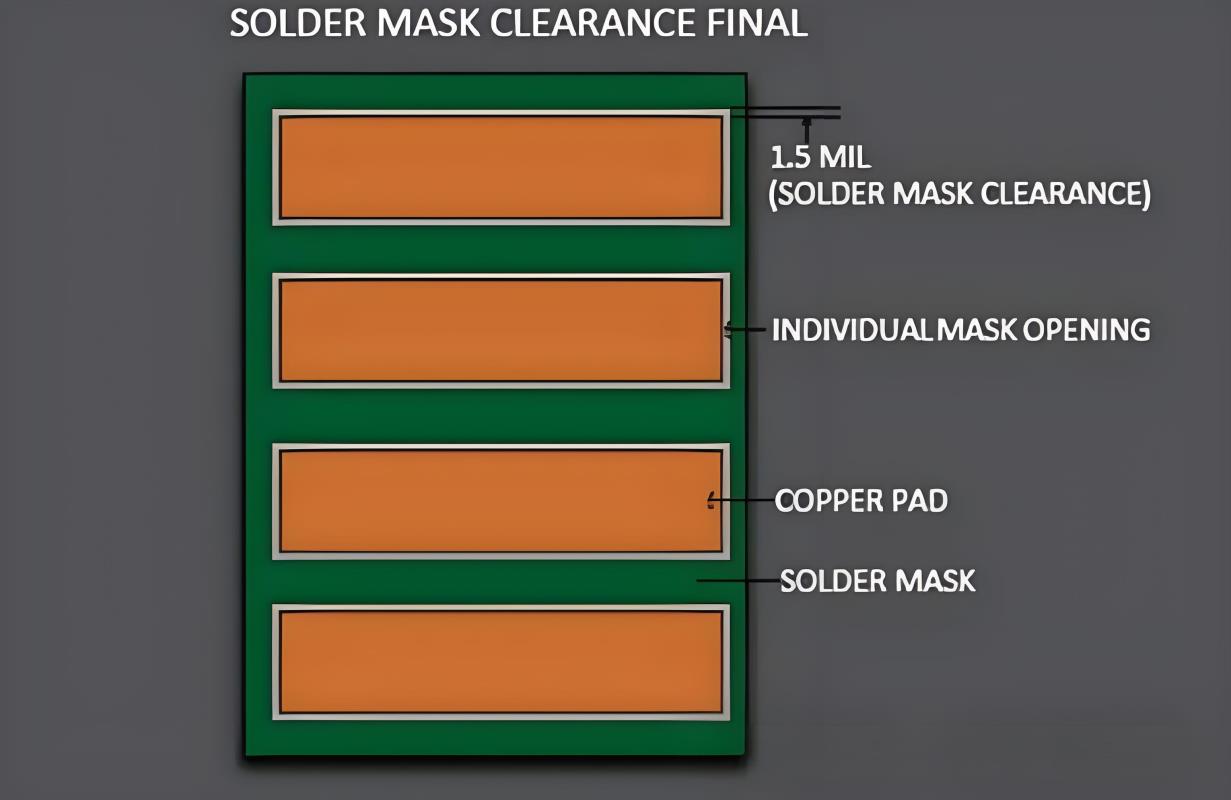

阻焊层是板表面的保护性涂层,防止污染和氧化。阻焊间隙(阻焊与焊盘等表面特征的距离)通常要求大于4mils。

值得注意的是阻焊对位问题,对位不良会导致阻焊重叠或部分暴露。根据工艺等级,标准工艺的对位要求为0.002",而高级和微工艺可达0.001"。

板表面上没有或不需要阻焊的区域称为阻焊Relief,常见于SMT焊盘、测试点和过孔周围。合理设计阻焊Relief能有效减少焊接过程中的墓碑效应。

PCB丝印设计:信息清晰与装配指导

丝印层使用非导电墨水标识元件、测试点、警告符号和Logo。清晰的丝印设计是高效组装和维修的基础。

丝印间距要求包括:丝印到阻焊间距≥4.5mils,丝印到铜间距≥6mils,丝印到孔/轮廓间距≥8mils。需特别注意,丝印不允许上焊盘,因为丝印若盖上焊盘,上锡时丝印处将不能上锡,从而影响元器件装贴。一般板厂要求预留8mil的间距,在紧密设计中至少也需保持4mil。

特定元件的DFM考量

0201元件的DFM挑战

在电子元器件小型化浪潮中,0201规格(0.6mm×0.3mm)无源元件对PCB设计、SMT工艺及DFM评估提出了严苛挑战。

焊盘设计是0201元件导入的首要环节。研究表明,焊盘横向延长、纵向缩短可显著降低墓碑效应。当焊盘中心间距控制在0.508mm(0.020~0.022inch)、边距为0.203mm(0.008~0.010inch)时,墓碑缺陷率可从12%降至0.3%。

模板设计同样关键。对于0201元件,推荐采用1:0.9的开口比例(较0402元件缩小10%),配合0.1mm厚度不锈钢模板,可实现脱模比率0.75~0.85。同时,焊膏选择Type5#焊膏(15~25μm)较Type4#(20~38μm)可提升印刷分辨率20%。

热焊盘与反焊盘的设计要点

在大面积的接地(电)中,元器件引脚与其连接需使用热焊盘(Thermal Relief)。热焊盘做成十字花焊盘形式,既满足电气性能需求,又减少了焊接时的散热问题,防止虚焊点的产生。

反焊盘(anti-pad)则在负片中定义铜皮与焊盘的距离。在高速PCB设计中,较大的反焊盘尺寸和较低的介电常数材料可以减少电容负载,从而提高过孔阻抗,减小传输延时。

经验设计值为:anti pad直径=regular pad直径+10mil,soldermask直径=regular pad直径+6~8mil,flash 内径=drill diameter+16mil,flash 外径=drill diameter+30mil。

PCB拼板与成本优化策略

拼板设计的经济效益

高多层PCB打样成本通常是普通板的3-5倍,合理的拼板设计可显著优化成本结构。

拼板数量优化公式为:最佳拼板数 = (大板尺寸/子板尺寸)× 利用率系数(高多层建议0.85)。例如,10层板子板尺寸5cm×5cm,选用30cm×30cm大板,最佳拼板数为(30×30)/(5×5)×0.85≈30片。

对于异形板,可将L型、圆形等高多层子板与矩形板混拼,填充边角废料区;采用“拼板旋转180°交错排列”,可提升材料利用率15%-20%。

DFM与成本的内在关联

通过DFM优化,企业可实现显著的成本节约。案例显示,某12层PCB项目通过拼板优化(利用率从60%提升至85%以上,并选用V割拼版),打样成本从8000元/批降至5500元/批,降幅达31.25%。

从更宏观的角度看,精益设计(DFMA)的23个降本增效原则包括简化零件、减少零件数量、标准化零部件、材料优化等。例如,特斯拉Model Y采用一体化压铸技术,将原本70多个零件组成的后底板变成1个铸件,成本降低40%,生产效率提升30%。

DFM检查清单:确保一次成功

在实际操作中,遵循系统的DFM检查清单能有效避免常见问题:

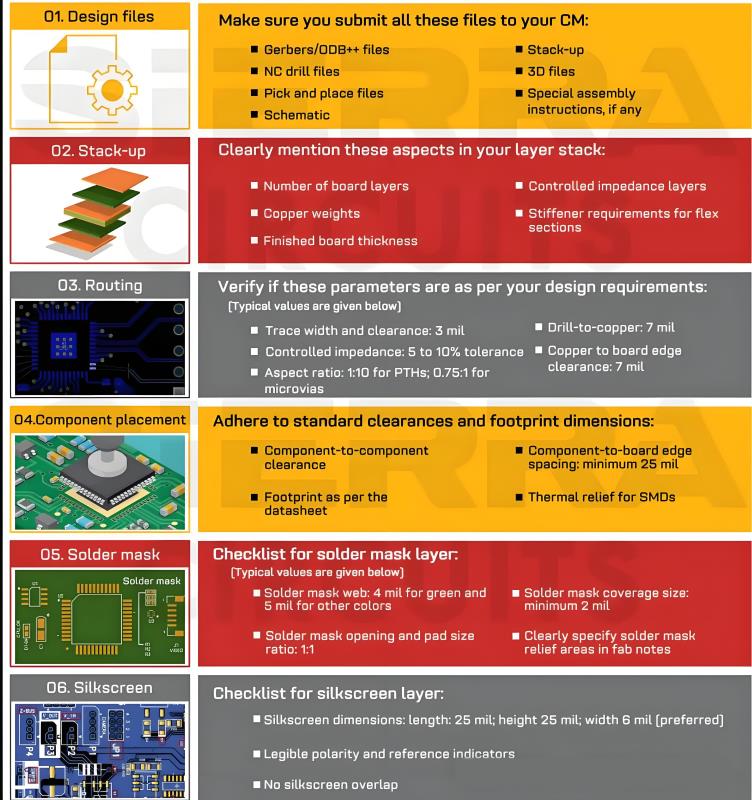

1. 制造文件完整性确认:Gerber/ODB++文件、NC钻孔文件、IPC 356A网表、元件放置文件(拾放)和PDF装配文件是否齐全?

2. 层压结构验证:确保层压顺序、厚度和介质材料符合设计要求和PCB生产厂家能力。

3. 钻孔工艺性检查:验证孔尺寸、位置和纵横比是否在制造商能力范围内。

4. 线路设计合理性:确认线宽线距、铜厚满足电气和制造要求。

5. 阻焊与丝印:检查阻焊开窗、丝印清晰度和位置精度。

6. 阻抗控制:核实阻抗线宽、间距和介质厚度是否符合要求。

7. 拼板设计:评估拼板方式、工艺边和定位孔设计。

8. 表面处理:选择适合产品应用场景的表面处理方式。

结语:DFM是设计与制造的无缝衔接桥梁

PCB可制造性设计不再是可有可无的选项,而是现代电子工程的基本要求。随着IPC-2221C等新标准的发布,行业对DFM的要求愈加严格和精细化。通过将DFM原则深度融入设计流程,工程师能够在保证质量的同时,显著降低制造成本,缩短产品上市时间。

在技术快速迭代的今天,优秀的PCB设计师不仅需要关注电气性能和功能实现,更要深刻理解制造工艺的边界与可能。只有设计与制造的无缝协作,才能在激烈的市场竞争中打造出既可靠又具成本优势的产品。