PCB高速信号设计终极指南:从识别到走线的7大黄金法则

发布时间:2025/6/3 15:53:40

在5G和AI芯片爆发的时代,高速信号设计正成为PCB工程师的核心竞争力。据IEEE数据,62%的电子设备故障源于高速信号完整性问题。当信号速率突破56Gbps,甚至向112Gbps演进时,传统的设计规则已无法满足需求。本文将揭秘高速PCB信号设计的核心法则,助您打造零失误的硬件系统。

一、高速PCB信号的本质:超越频率的认知革命

1.1 物理定义与判定标准

高速信号的本质是边沿速率主导而非频率高低。核心判定公式:

Tr ≤ 6 × Td

▌其中:

· Tr = 信号上升时间(10%~90%)

· Td = 信号传输延迟(ps/inch)

示例:FR4板材中信号传播速度≈6ps/mm,若走线长度150mm,则Td=900ps。当信号Tr≤5.4ns时即属高速信号。

1.2 高速与高频的临界误区

▌关键区别:

· 高频信号:关注频域特性(>50MHz)

· 高速信号:关注时域边沿(Tr<1ns)

血泪教训:某无人机主控电路板因忽略DDR4的0.35ns上升沿(尽管仅1600MHz),导致眼图塌陷损失超$2M。

二、高速信号识别四步法:EDA工程师实战手册

2.1 接口类型快速定位

2.2 八大高速接口阻抗表

|

接口类型 |

差分阻抗(Ω) |

单端阻抗(Ω) |

速率阈值 |

|

USB 3.2 |

85±5% |

90±10% |

10Gbps |

|

HDMI 2.1 |

100±5% |

- |

48Gbps |

|

PCIe 5.0 |

85±3% |

- |

32GT/s |

|

DDR5 |

- |

40±5% |

6400MT/s |

|

MIPI C-PHY |

100±10% |

- |

6Gsps |

|

SATA III |

100±5% |

- |

6Gbps |

|

LVDS |

100±10% |

- |

3.125Gbps |

|

25G Ethernet |

100±5% |

- |

25.78Gbps |

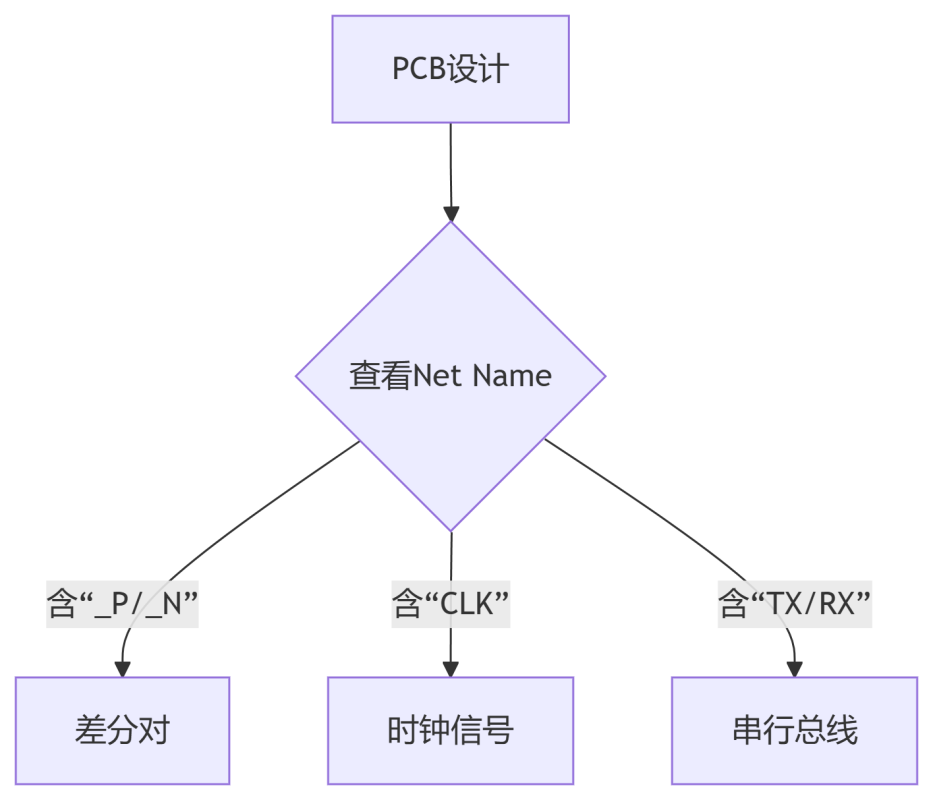

2.3 原理图无权限时的破解技巧

· 网络名特征识别:

o MIPI:MIPI_D0P/N,MIPI_CLK_P/N

o PCIe:PCIe_TX_P/N,PCIe_RX_P/N

· 器件引脚定位:

o FPGA的Bank1/2通常配置高速接口

o 连接器区域90%存在高速信号

2.4 拓扑结构预判法

三、高速PCB走线7大黄金法则:超越3W原则的实战技巧

3.1 PCB阻抗控制三要素

微带线阻抗公式:

Z0 = 87 / √(εr+1.41) × ln(5.98H / (0.8W+T))

▌参数说明:

· εr:介质常数(FR4≈4.2)

· H:信号层到参考层距离(mil)

· W:走线宽度(mil)

· T:铜厚(oz)

案例:USB3.1要求85Ω,当H=5mil时,W≈4.2mil(1oz铜厚)

3.2 等长匹配进阶策略

|

信号类型 |

等长公差 |

相位补偿技巧 |

|

DDR5数据线 |

±2mil |

蛇形绕线间距≥3W |

|

PCIe Gen4 |

±5mil |

换层处加补偿电容 |

|

HDMI差分对 |

±10mil |

避免90°拐角 |

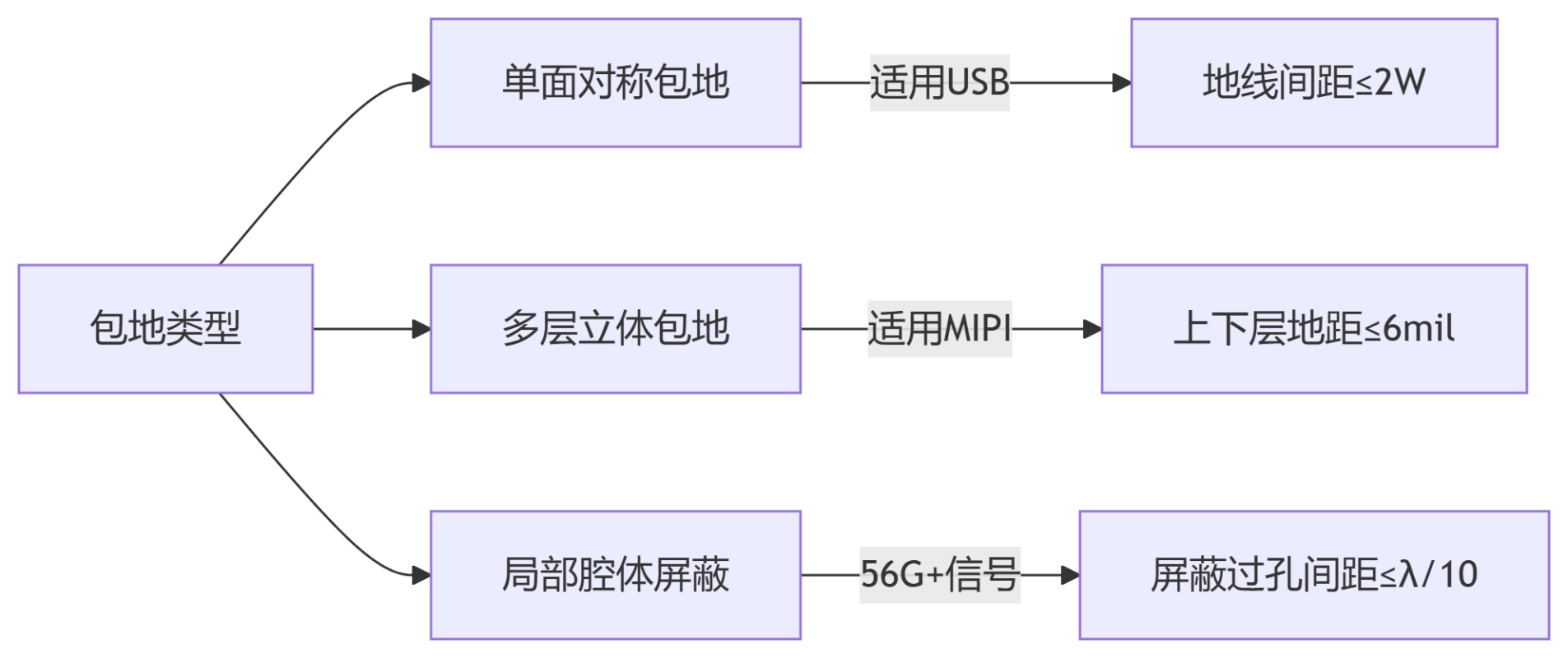

3.3 立体包地技术矩阵

3.4 玻纤效应破解方案

PCB高速板材玻纤编织导致阻抗±8%波动,应对措施:

1. 角度偏移:走线与玻纤方向成15°夹角

2. 交叉铺层:选用1080/1035等细编织材料

3. 填胶处理:采用低玻纤峰谷差材料(如Megtron6)

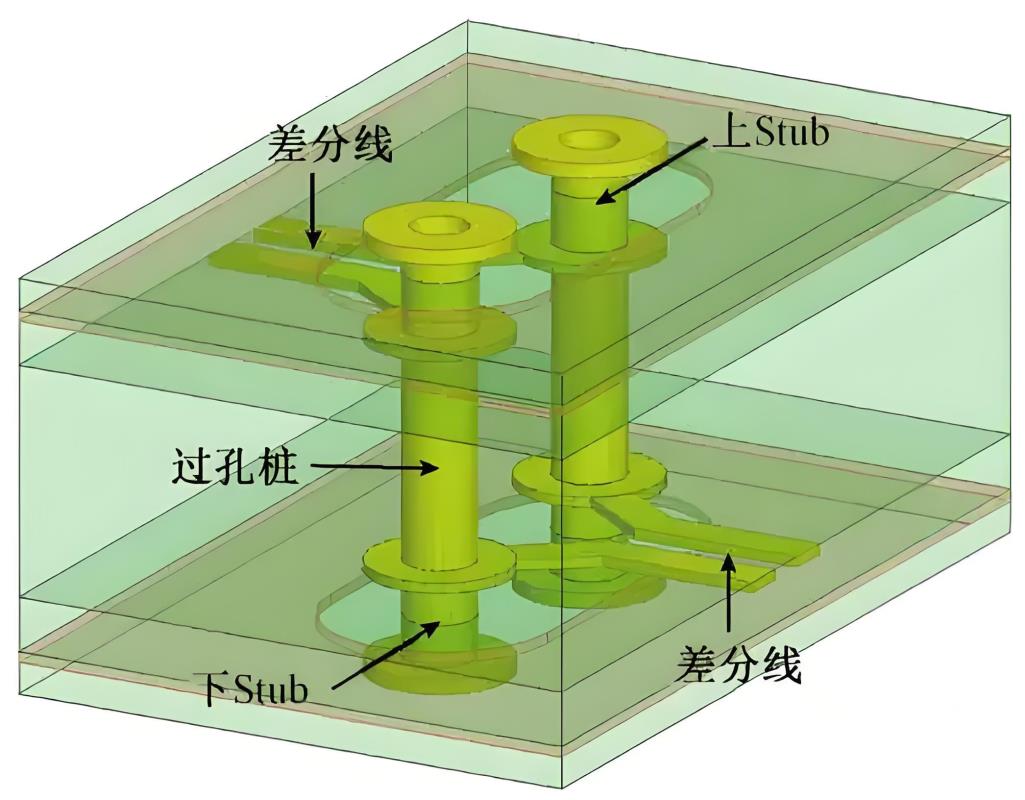

3.5 PCB过孔优化三维模型

· 反钻工艺:残留stub长度≤信号波长1/20(112G需<5mil)

· 背钻深度:目标层+8mil误差控制

· 地孔阵列:换层处1:4信号地孔比

四、PCB信号完整性验证:从规则驱动到仿真驱动

4.1 必备仿真项目清单

1. 时域反射分析(TDR) → 阻抗连续性检测

2. 眼图测试 → 模板裕量≥15%

3. 串扰分析 → 近端<5%,远端<3%

4. 电源完整性 → 目标阻抗Z<1mΩ

4.2 实测vs仿真容差表

| 参数 | 仿真要求 | 实测允差 | 失效风险点 |

|---|---|---|---|

| 插入损耗 | <-3dB@Nyquist | ±0.5dB | 玻纤效应区 |

| 回波损耗 | >-10dB | ±2dB | 连接器处 |

| 抖动 | <0.15UI | ±0.02UI | 时钟路径 |

行业趋势:Ansys HFSS 2023实测显示,采用AI预布局可使PCB设计迭代减少70%

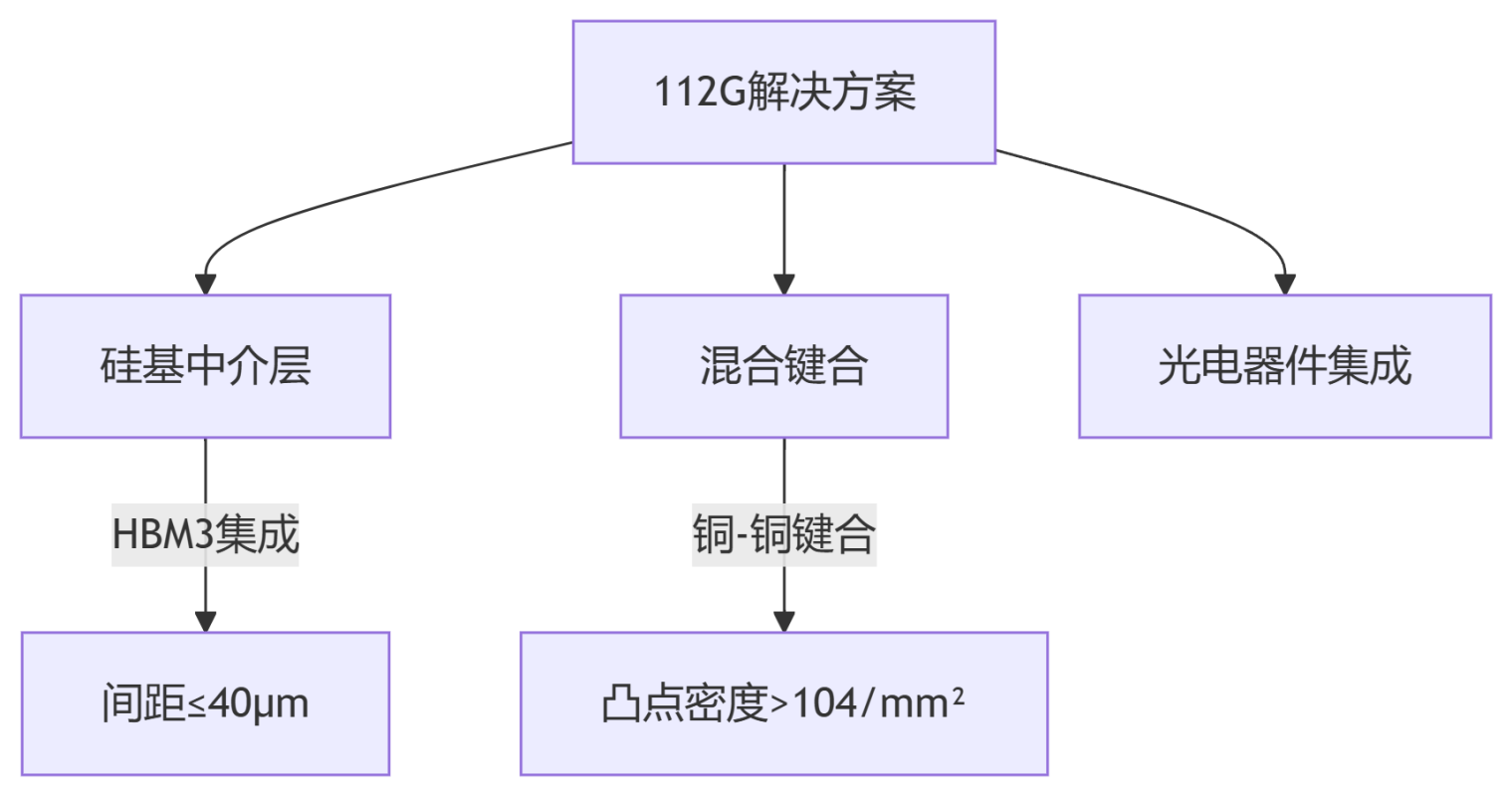

五、未来挑战:112G PAM4设计预警

5.1 PCB新材料革命

|

材料类型 |

Dk@10GHz |

Df@10GHz |

适用速率 |

|

Megtron8 |

3.0±0.05 |

0.0012 |

112Gbps |

|

Tachyon100G |

3.2±0.03 |

0.0015 |

224Gbps |

|

改性PTFE |

2.5±0.02 |

0.0008 |

400Gbps+ |

5.2 三维集成技术

结语:高速设计的本质是电磁场博弈

当信号速率突破112Gbps,PCB设计已进入“微观电磁世界”。成功的秘诀在于:

1. 精准预判:早期识别高速信号网络

2. 三维控制:从平面走线到立体场管理

3. 协同仿真:SI/PI/EMC联合优化

4. 材料革命:拥抱低Df介质新材料

工程师箴言:在高速PCB设计领域,0.1mm的走线偏移可能颠覆整个系统。唯有掌握电磁法则,方能在数字洪流中搭建稳固的信息桥梁。